# Radiation Hardened High Speed Dual Voltage Comparators

# ISL7119RH, ISL7119EH

The ISL7119RH, ISL7119EH are radiation hardened, high speed, dual voltage comparators fabricated on a single monolithic chip. They are designed to operate over a wide dual supply voltage range as well as a single 5V logic supply and ground. The open collector output stage facilitates interfacing with a variety of logic devices and has the ability to drive relays and lamps at output currents up to 25mA.

The ISL7119RH, ISL7119EH are fabricated on our dielectrically isolated Rad-hard Silicon Gate (RSG) process, which provides immunity to Single Event Latch-up (SEL) and highly reliable performance in the natural space environment.

Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed below must be used when ordering.

Detailed Electrical Specifications for the ISL7119RH, ISL7119EH are contained in SMD 5962-07215. A "hot-link" is provided on our website for downloading.

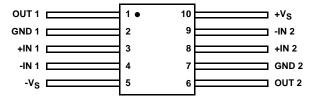

# **Pin Configuration**

ISL7119RH, ISL7119EH (10 LD FLATPACK GDFP1-F10 OR CDFP2-F10) TOP VIEW

## **Features**

- Electrically Screened to DLA SMD # 5962-07215

- QML Qualified Per MIL-PRF-38535 Requirements

- Radiation Environment

|   | Total Dose                                                                   |

|---|------------------------------------------------------------------------------|

|   | SEL/SEB Immune                                                               |

| • | nput Offset Voltage (V <sub>IO</sub> ) 8mV (Max)                             |

| • | nput Bias Current (I <sub>BIAS</sub> ) 1000nA (Max)                          |

| • | nput Offset Current (I <sub>IO</sub> )150nA (Max)                            |

| • | Saturation Voltage @ $I_{SINK}$ = 3.2mA ( $V_{SAT}$ ) 0.65V (Max)            |

| • | Saturation Voltage @ I <sub>SINK</sub> = 25mA (V <sub>SAT</sub> ) 1.8V (Max) |

| • | Response Time (t <sub>PD</sub> )                                             |

# **Applications**

- Window Detector

- · Level Shifter

- · Relay Driver

- Lamp Driver

# **Ordering Information**

| ORDERING NUMBER   | INTERNAL<br>MKT. NUMBER | PART<br>MARKING     | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free)                | PKG.<br>DWG. # |

|-------------------|-------------------------|---------------------|---------------------|-------------------------------------|----------------|

| 5962F0721501QXC   | ISL7119RHQF (Note)      | Q 5962F07 21501QXC  | -55 to +125         | 10 Lead Ceramic Metal Seal Flatpack | K10.A          |

| 5962F0721501VXC   | ISL7119RHVF (Note)      | Q 5962F07 21501VXC  | -55 to +125         | 10 Lead Ceramic Metal Seal Flatpack | K10.A          |

| 5962F0721502VXC   | ISL7119EHVF (Note)      | Q 5962F07 21502VXC  | -55 to +125         | 10 Lead Ceramic Metal Seal Flatpack | K10.A          |

| 5962F0721501V9A   | ISL7119RHVX             |                     | -55 to +125         | 10 Lead Ceramic Metal Seal Flatpack | K10.A          |

| 5962F0721502V9A   | ISL7119EHVX             |                     | -55 to +125         | 10 Lead Ceramic Metal Seal Flatpack | K10.A          |

| ISL7119RHF/Proto  | ISL7119RHF/Proto (Note) | ISL7 119RHF / Proto | -55 to +125         | 10 Lead Ceramic Metal Seal Flatpack | K10.A          |

| ISL7119RHX/Sample | ISL7119RHX/Sample       | Die                 |                     | •                                   | •              |

NOTE: These Intersil Pb-free Hermetic packaged products employ 100% Au plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

## **ISL7119RH, ISL7119EH**

## **Die Characteristics**

## **DIE DIMENSIONS:**

2030 $\mu$ m x 2030 $\mu$ m (~80 mils x 80 mils) Thickness: 483 $\mu$ m  $\pm$  25.4 $\mu$ m (19 mils  $\pm$  1 mil)

#### **INTERFACE MATERIALS:**

#### **Glassivation:**

Type: PSG (Phosphorous Silicon Glass)

Thickness: 8.0kÅ ± 1.0kÅ

## **Top Metallization:**

Type: AlSiCu

Thickness: 16.0kÅ ± 2kÅ

#### **Substrate:**

Radiation Hardened Silicon Gate. Dielectric Isolation

#### **Backside Finish:**

Silicon

## **ASSEMBLY RELATED INFORMATION:**

#### **Substrate Potential:**

Unbiased (DI)

#### **ADDITIONAL INFORMATION:**

## **Worst Case Current Density:**

$< 2.0 \times 10^5 \text{ A/cm}^2$

## **Transistor Count:**

66

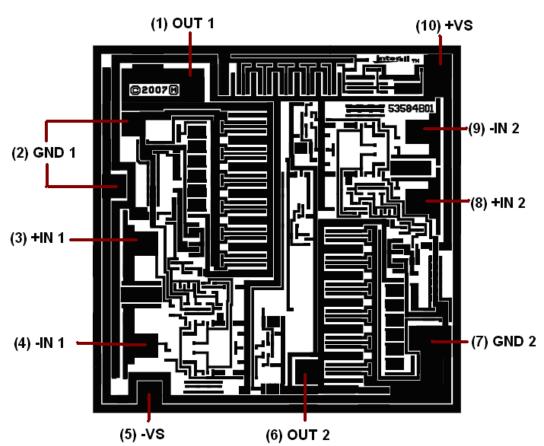

# **Metallization Mask Layout**

ISL7119RH, ISL7119EH

For additional products, see <a href="https://www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

intersil